FPGAemu

Download: fpgaemu-1.3.tar.gz

Repository: https://github.com/fabian-l-c/fpgaemu

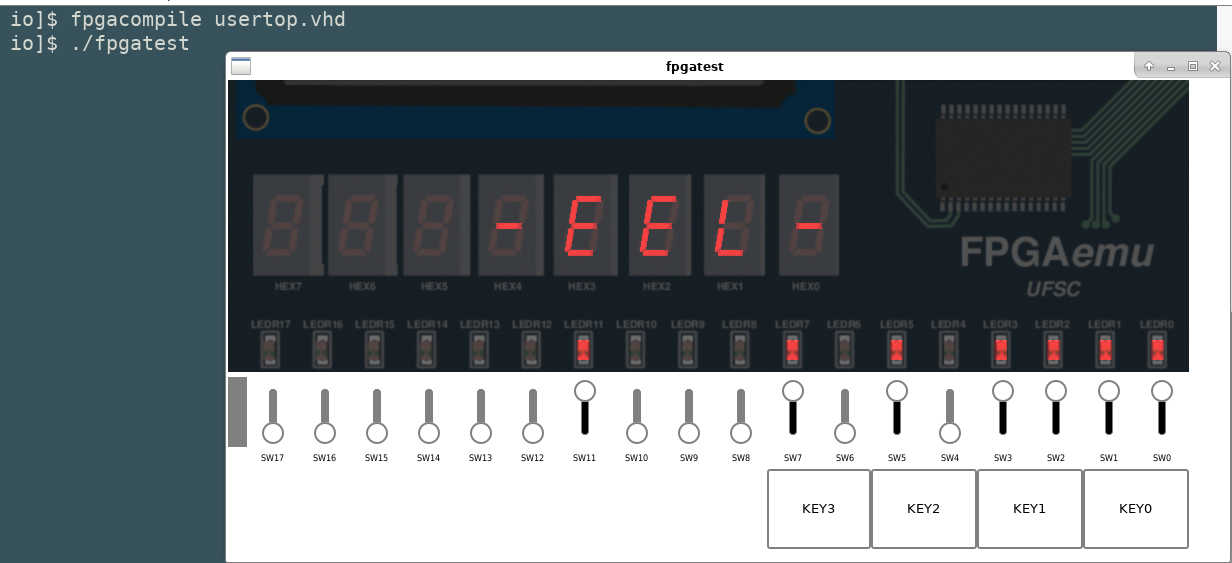

- FPGAemu é o emulador de uma placa genérica baseada em FPGA visando o ensino de conceitos básicos sobre projeto de circuitos digitais. FPGAemu foi desenvolvido por Fabian L. Cabrera em 2020 para permitir a realização de práticas remotas na disciplina “EEL5105 – Circuitos e técnicas digitais” durante a pandemia.

-

- Requisitos

ghdl (com GCC ou LLVM back-end)*

gtk3

pthread

icarus verilog (Novo, para suporte a verilog)

*O emulador não pode ser usado com o back-end do ghdl mcode. Para mais informação visite:

https://steveicarus.github.io/iverilog/

Ubuntu:

sudo apt-get install build-essential make gnat libgtk-3-dev libpthread-stubs0-dev ghdl-llvm

-

- Instalação

Descarregue a última versão. Depois descompacte, configure e instale com os seguintes comandos:

tar xvfz fpgaemu-1.3.tar.gz

cd fpgaemu-1.3

./configure

make

make install

Nota: se ghdl está instalado em uma pasta não-padronizada (por exemplo: /opt/local/bin), ela pode ser informada na linha de comando de configuração:

./configure –with-ghdl=/opt/local/bin/ghdl

-

- Usando o FPGAemu com VHDL

Copie a pasta de exemplos na sua área de trabalho e use os comandos:

cd examples/io

fpgacompile usertop.vhd

./fpgatest

O mesmo procedimento pode ser aplicado aos exemplos “register” e “counter”.

O arquivo VHDL principal sempre deve ter o nome “usertop.vhd”. Também as definições de portas de “usertop.vhd” devem ser mantidas iguais sempre:

CLOCK_50: Não usado, sempre igual a ‘0’;

CLK_500Hz: Sinal de relógio de 500Hz;

RKEY: Igual a KEY;

KEY: Quatro botões de entrada (‘0’-pressionado, ‘1’-solto);

RSW: Igual a SW;

SW: Dezoito chaves de entrada;

LEDR: Dezoito LEDs vermelhos de saída;

HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7 : Oito displays sete-segmentos.

Em caso de múltiplos arquivos VHDL, eles devem ser listados seguindo a ordem hierarquica. Por exemplo, se “block.vhd” é um componente usado em “usertop.vhd” então os comandos para rodar o emulador devem ser:

fpgacompile block.vhd usertop.vhd

./fpgatest

-

- Usando o FPGAemu com verilog

Copie a pasta de exemplos na sua área de trabalho e use os comandos:

cd vexamples/io

vfpgacompile usertop.v

./vfpgatest

O mesmo procedimento pode ser aplicado aos exemplos “register” e “counter”.

O módulo verilog principal sempre deve ter o nome “usertop”. Também as definições de portas de “usertop.v” devem ser mantidas iguais sempre:

CLOCK_50: Não usado, sempre igual a ‘0’;

CLK_500Hz: Sinal de relógio de 500Hz;

RKEY: Igual a KEY;

KEY: Quatro botões de entrada (‘0’-pressionado, ‘1’-solto);

RSW: Igual a SW;

SW: Dezoito chaves de entrada;

LEDR: Dezoito LEDs vermelhos de saída;

HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7 : Oito displays sete-segmentos.

Em caso de múltiplos arquivos verilog, eles devem ser listados seguindo a ordem hierarquica. Por exemplo, se “block.v” é um componente usado em “usertop.v” então os comandos para rodar o emulador devem ser:

vfpgacompile block.v usertop.v

./vfpgatest

-

- Referências