FPGAemu

Download: fpgaemu-1.3.tar.gz

Repository: https://github.com/fabian-l-c/fpgaemu

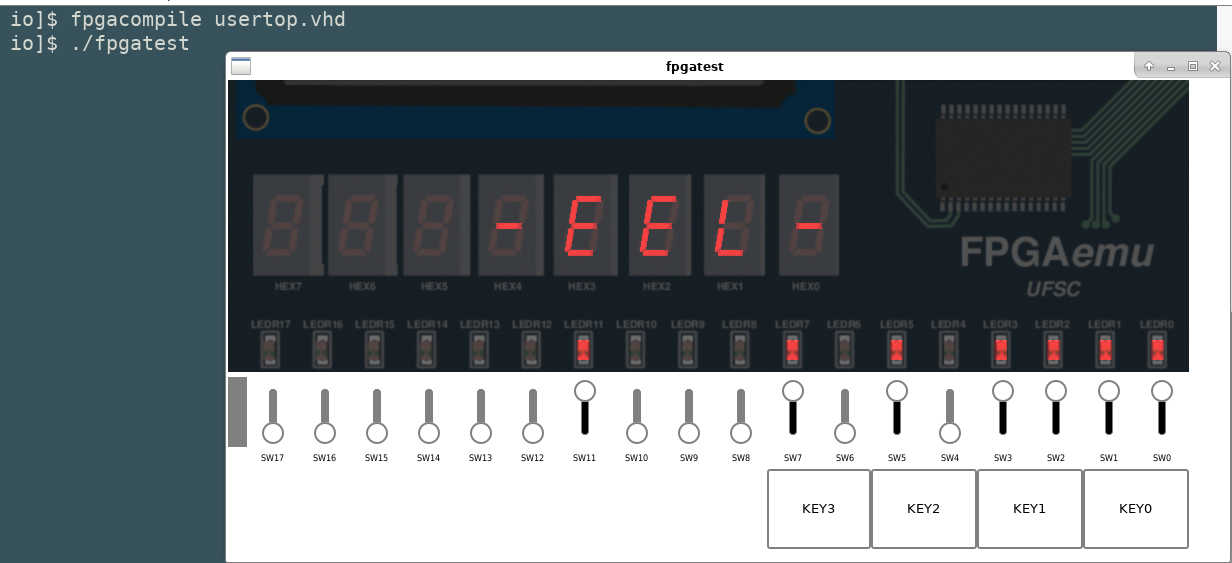

- FPGAemu is the emulator of a generic FPGA-based board intended for teaching basics of digital circuits design. FPGAemu was developed by Fabian L. Cabrera in 2020 to allow remote practices of the course “EEL5105 – Digital circuits and techniques” during the pandemic.

-

- Requirements

ghdl (with GCC or LLVM back-end)*

gtk3

pthread

icarus verilog (New for verilog support)

*Note that the emulator can not be used with the ghdl mcode back-end. For more information visit:

https://steveicarus.github.io/iverilog/

Ubuntu:

sudo apt-get install build-essential make gnat libgtk-3-dev libpthread-stubs0-dev ghdl-llvm

-

- Installation

Download the latest release. Uncompress, configure and install with the following commands:

tar xvfz fpgaemu-1.3.tar.gz

cd fpgaemu-1.3

./configure

make

make install

Note: if ghdl is installed in a non-standard path (for example: /opt/local/bin), it can be informed in the configure line command:

./configure –with-ghdl=/opt/local/bin/ghdl

-

- Using FPGAemu with VHDL:

Copy the examples folder to your home directory and use the commands:

cd examples/io

fpgacompile usertop.vhd

./fpgatest

Same procedure can be used to run the “register” and “counter” examples.

The main VHDL file always must be named “usertop.vhd”. Also the port definitions of “usertop.vhd” must be always kept the same:

CLOCK_50: Not used, always equal to ‘0’;

CLK_500Hz: 500Hz clock signal;

RKEY: Equal to KEY;

KEY: Four-buttons input (‘0’-pressed, ‘1’-released);

RSW: Equal to SW;

SW: Eighteen input switches;

LEDR: Eighteen output red LEDs;

HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7 : Eight seven-segments displays.

In case of multiple VHDL files, they must be listed following a hierarchical order. For example, if “block.vhd” is a component used in “usertop.vhd” then the commands to run the emulator must be:

fpgacompile block.vhd usertop.vhd

./fpgatest

-

- Using FPGAemu with verilog:

Copy the examples folder to your home directory and use the commands:

cd vexamples/io

vfpgacompile usertop.v

./vfpgatest

Same procedure can be used to run the “register” and “counter” examples.

The main verilog module always must be named “usertop”. Also the port definitions of “usertop.v” must be always kept the same:

CLOCK_50: Not used, always equal to ‘0’;

CLK_500Hz: 500Hz clock signal;

RKEY: Equal to KEY;

KEY: Four-buttons input (‘0’-pressed, ‘1’-released);

RSW: Equal to SW;

SW: Eighteen input switches;

LEDR: Eighteen output red LEDs;

HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7 : Eight seven-segments displays.

In case of multiple verilog files, they must be listed following a hierarquical order. For example, if “block.v” is a component used in “usertop.v” then the commands to run the emulator must be:

vfpgacompile block.v usertop.v

./vfpgatest

-

- References